# PATENT ABSTRACTS OF JAPAN

(11)Publication number:

05-235718

(43) Date of publication of application: 10.09.1993

(51)Int.Cl.

HO3K 5/156 HO3K 5/135

(21)Application number: 04-030530

(71)Applicant : ADVANTEST CORP

(22)Date of filing:

18.02.1992

(72)Inventor: TOMITA YOSHIETSU

**HIGUCHI KENJI**

## (54) JITTER PROVISION DEVICE

# (57)Abstract:

PURPOSE: To provide the litter provision device providing jitter and a phase delay simultaneously. CONSTITUTION: This device is provided with a digital delay circuit 10 comprising an n-stage shift register 11 receiving a digital signal and an n-to-1 selector 12 receiving an output of the shift register 11 to its relevant input and allowing the n-to-1 selector 12 to selectively output a digital signal with an optional delay among digital signals delayed by the shift register 11, with a clock A signal source advancing the shift register 11, with a frequency divider 20 applying 1/N frequency division to the clock A, with an address counter 30 advanced by the frequency division output, and with a RAM 40 in which data representing a content of jitter are described, addressing the RAM data based on the description content of the counter 30 and outputting the addressed signal to the n-to-1 selector 12 as a selection signal.

# (19)日本国特許庁(JP)

# (12) 公開特許公報(A)

(11)特許出願公開番号

# 特開平5-235718

(43)公開日 平成5年(1993)9月10日

(51)Int.Cl.<sup>5</sup>

識別記号

庁内整理番号

FΙ

技術表示箇所

H 0 3 K 5/156 5/135 A 7402-5 J

4239-5 J

審査請求 未請求 請求項の数1(全 5 頁)

(21)出願番号

(22)出願日

特願平4-30530

平成 4年(1992) 2月18日

(71)出願人 390005175

株式会社アドバンテスト

東京都練馬区旭町1丁目32番1号

(72)発明者 富田 義悦

東京都練馬区旭町 1 丁目32番 1 号 株式会

社アドバンテスト内

(72)発明者 樋口 憲二

東京都練馬区旭町1丁目32番1号 株式会

社アドバンテスト内

(74)代理人 弁理士 草野 卓 (外1名)

## (54) 【発明の名称 】 ジッタ付与装置

#### (57) 【要約】

【目的】 ジッタおよび位相遅延を同時に付与するジッタ付与装置を提供する。

【構成】 ディジタル信号が入力されるn段シフトレジスタ11と、シフトレジスタ11の出力が対応する入力に接続するntolセレクタ12とを有して、シフトレジスタ11により遅延せしめられたディジタル信号の遅延量のディジタル信号をntolセレクタ12により選択出力するディジタル遅延回路10を具備し、シフトレジスタ11を歩進するクロックA信号源し、シフトレジスタ11を歩進するクロックA信号源し、シフトレジスタ11を歩進するクロックA信号源し、シフトレジスタ11を歩進するクロックA信号源値し、クロックAを1/N分周する分周器20を具備し、分周出力により歩進されるアドレス・カウンタ30の記述内容によりアドレスRAMデータをカウンタ30の記述内容によりアドレスRAM番で見備するジッタ付与装置。

#### 【特許請求の範囲】

【請求項1】 ディジタル信号が入力されるn段シフトレジスタと、n段シフトレジスタの出力が対応する入力に接続するnラインtolライン・セレクタとを有してn段シフトレジスタにより遅延せしめられたディジタにより遅延せしめられたディジタル信号の内の任意の遅延量のディジタル信号をnライン・セレクタにより選択しびスタを歩進するでいた。カウンタを具備し、クロックAを1/Nの周器を具備し、クロックAを1/Nの周器を具備し、分周出力により歩進されてこのRAMデータをアドレス・カウンタを具備し、ジッタ内容を示すデータが記述されてこのRAMデータをアドレス・カウンタが記述されてこのRAMデータをアドレス・カウンタで記述されてこのRAMデータをアドレス・カウンタで記述されてこのRAMデータをアドレス・カウイン・セレクタに出力するRAMを具備することを特徴とするジッタ付与装置。

#### 【発明の詳細な説明】

#### [0001]

【産業上の利用分野】この発明は、ジッタ付与装置に関し、特に、ディジタル信号の遅延回路を使用してジッタおよび位相遅延を同時に付与するジッタ付与装置に関する。

### [0002]

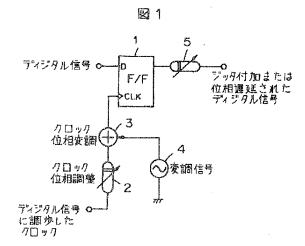

《従来の技術》 ジッタ付与装置の従来例を図1を参照し て説明する。図1において、1はフリップ・フロップで あり、そのデータ端子口にディジタル信号が供給される 一方、そのクロック端子CLKにはクロックが送り込ま れる。ここで、このクロックについてであるが、これは ディジタル信号に同期したクロックをクロック位相遅延 調整器2に供給してここにおいてクロックの位相遅延調 整をし、位相遅延調整されたクロックをクロック位相変 調器3にかけてここにおいて変調信号源4から送り出さ れる変調信号により位相変調した結果のものである。結 周、フリップ・フロップ1から送り出される出力は上述 の渦りに位相遅延調整および位相変調されたクロックに よりリタイミングされたディジタル信号であり、ここに おいてジッタおよび位相遅延が付与されたディジタル信 号が得られたことになる。このジッタおよび位相遅延が 付与されたディジタル信号は遅延線その他の微小遅延素 子5を介して出力される。

#### [00003]

【発明が解決しようとする課題】この従来のジッタ付与 装置は、クロック位相変調器3と変調信号源4とより成 るジッタ付与回路とクロック位相遅延調整器2とが別体 で独立していて、装置として効率がよくない。ジッタ付 与回路はそのジッタ周波数、振幅、波形を調整制御可能 なものに構成しようとすると、クロック位相変調器3お よび変調信号源4の規模は大きなものとなる。

《 O O O 4 》 そして、この従来のジッタ付与装置はディジタル信号に同期したクロック信号源を特に具備しなければならない。この発明は、上述の通りの問題を解消し

たジッタ付与装置を提供するものである。

#### [0005]

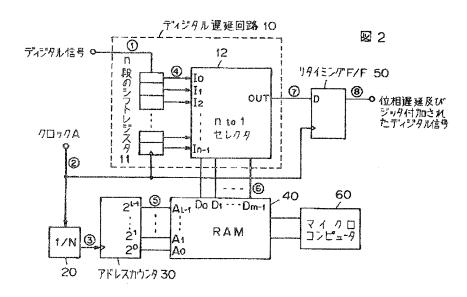

**【課題を解決するための手段】ディジタル信号が入力さ** れるn段シフトレジスタ11と、n段シフトレジスタ1 1の出力が対応する入力 I 0 、 I 1 、 I 2 ・・・ I n-1 に接続するnラインto1ライン・セレクタ12とを有 して、n段シフトレジスタ11により遅延せしめられた ディジタル信号の内の任意の遅延量のディジタル信号を n ライン t o 1 ライン・セレクタ 1 2 により選択して出 力するディジタル遅延回路10を具備し、n段シフトレ ジスタ11を歩進するクロックA信号源を具備し、クロ ックAを1/N分周する分周器20を具備し、分周器2 0の分周出力により歩進されるアドレス・カウンタ30 を具備し、ジッタ内容を示すデータが記述されてこのR AMデータをアドレス・カウンタ30の記述内容により アドレスして選択信号としてnラインtolライン・セ レクタ12に出力するRAM40を具備することを特徴 とするジッタ付与装置を構成した。

#### [0006]

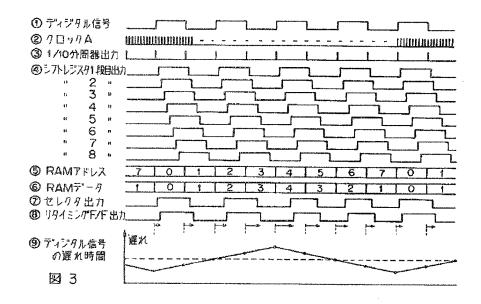

【実施例】この発明の実施例を図2を参照して説明する。図2において、ディジタル遅延回路10は入力されるディジタル信号をクロックAの1周期づつ最大 n周期迄遅延することができる遅延回路である。このディジタル遅延回路10は、ディジタル信号はn段シフトレジスタ11に入力され、n段シフトレジスタ11に入力されて、n段シフトレジスタ11により遅延せしめられたディジタル信号の内の任意の遅延量のディジタル信号をnラインto1ライン・セレクタ12により選択して出力するものである。

【0007】ここで、クロック信号源から送り込まれるクロックAはディジタル遅延回路10の遅延分解能を決定するクロックであり、ディジタル信号のビット・レートより高い繰り返し周波数に選択される。クロックAの周期は遅延分解能そのものである。例えば、遅延分解能をディジタル信号のビット・レートの1%であるものとすると、クロックAの繰り返し周波数はディジタル信号のビット・レートの100倍としなければならない。

【0008】 nラインto1ライン・セレクタ12によりn個の入力の内の1個を選択するためには、セレクタ12の選択信号線の本数mは、2m ≧n としなければならない。例えば、m=3、n=8 とされる。1/N分周器20はジッタの周期を1/Nにするために具備されている。このNを変更することにより、最短のジッタ周期からそのN倍のジッタ迄のジッタ周期の調整をすることができる。

【0009】アドレス・カウンタ30のビット数 I はジッタの周期により決定される。例えば、クロックA16サイクルで1周期のジッタを加えるには、このカウンタ

は16進カウンタである必要があり、1=4としなければならない。40はRAMであり、例えば次の如きジッタ内容を示すデータをマイクロ・コンピュータ60により書き込む。

【0010】リタイミング・フリップ・フロップ50は nラインto1ライン・セレクタ12を切り換える時に 発生するスパイクを抑圧するために具備されたものであ り、これが問題とされない場合は具備する必要はない。 図2のタイミング・チャートを参照してこの発明の動作 説明をする。ここで、

シフトレジスタ数 : n=8RAMデータ線本数 : m=3RAMアドレス線本数: I=3分周比 : N=10

クロック A : ディジタル信号のビット・レー

トの10倍の周波数

とする。

【0011】要するに、アドレス・カウンタ30の内容に応じて、RAM40からディジタル遅延回路10のnラインto1ライン・セレクタ12へ選択信号であるRAMデータが供給される。nラインto1ライン・セレクタ12は、このRAM40のデータの書き込み内容に応じて、n段シフトレジスタ11の出力の内から何れか1本の出力を選択する。RAM40のデータの書き込み内容は下記の通りである。

#### [0012]

| <b>RAMアドレス</b> | RAMデータ |

|----------------|--------|

| 0              | 0      |

| 1              | 1      |

| 2              | 2      |

| 3              | 3      |

| 4              | 4      |

| 5              | 3      |

| 6              | 2      |

| 7              | 7      |

この場合の n ライン t o 1 ライン・セレクタ 1 2 の出力はのに示される通りになる。即ち、アドレス=0 の時、データ=0 というのであるから、元のディジタル信号からの遅延が零のシフトレジスタ 1 段目の出力が選択出力がった。シフトレジスタ 1 段目の出力は、データーはそれを基準とする)。アドレス=1 の時、データー 2 の時、データ=2 というのであるから遅延がクロック A の 1 周期分であるのシフトレジスタ 2 段目の出力が選択出力される。以下、ロック A の 2 周期分であるから遅延がクロック A の 2 周期分であるから遅延がクロック A の 2 周期分であるから遅延がクロック A の 1 周期分であるから遅延がクロック A の 1 周期分であるのシフトレジスタ 2 段目の出力が選択出力される。そして、のに示されるセレクタ出力はリタイ

ミング・フリップ・フロップ50を介して圏として出力される。ここで、元のディジタル信号からの遅延であるリタイミング・フリップ・フロップ50の出力を縦軸にとって示すとこれは⑨に示される如くになる。このジッタの内容は、中心となる位相遅延はクロックAの4周期分、ジッタ振幅はピーク・ピーク値でクロックAの4周期分、そしてジッタ周期はクロックAの80周期分の三角波ジッタである。

【0013】RAM40のデータの書き込み内容を下記の通りに変更してみる。

| RAMアドレス | RAMデータ |

|---------|--------|

| 0       | 6      |

| 1       | 7      |

| 2       | 7      |

| 3       | 6      |

| 4       | 4      |

| 5       | 3      |

| 6       | 3      |

| 7       | 4      |

|         |        |

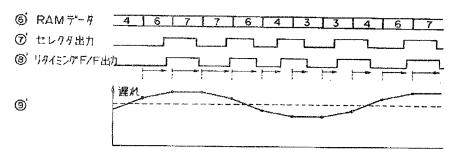

この場合のセレクタ12の出力およびリタイミング・フリップ・フロップ50の出力は⑦ および⑧ に示される通りである。リタイミング・フリップ・フロップ50の出力® を縦軸に遅延をとって示すと⑨ に示される如くになる。このジッタの内容は、中心となる位相遅延はクロックAの7周期分、ジッタ振幅はピーク・ピーク値でクロックAの14周期分、そしてジッタ周期はクロックAの80周期分の近似正弦波波ジッタである。

#### [0014]

【発明の効果】以上の通りであって、この発明のジッタ付与装置は、位相遅延とジッタの付与とを同時に実現することができるものであり、RAM40のデータの記述内容に対応した位相遅延量、ジッタ量およびジッタ波形を実現することができる。この記述内容の変更はマイクロ・コンピュータにより容易に実行することができる。そして、ディジタル信号に同期したクロック源を特に具備する必要もない。

#### 【図面の簡単な説明】

【図1】ジッタ付与装置の従来例を示す図。

【図2】この発明の実施例を示す図。

【図3】この発明の実施例のタイミング・チャート。

【図4】この発明の実施例の他のタイミング・チャート。

#### 【符号の説明】

10 ディジタル遅延回路

11 n段シフトレジスタ

12 nラインto1ライン・セレクタ

A クロックA信号源

20 1/N分周器

30 アドレス・カウンタ

40 RAM

【図1】

[図2]

[図4]

図 4

#### [図3]

#### 【手続補正書】

【提出日】平成5年1月6日

## 【手続補正1】

【補正対象書類名】明細書

〖補正対象項目名』0008

【補正方法】変更

#### 【補正内容】

#### 【手続補正2】

〖補正対象書類名》明細審

【補正対象項目名】0013

【補正方法】変更

【補正內容】

【0013】RAM40のデータの書き込み内容を下記

#### の通りに変更してみる。

| RAMアドレス | RAMデータ |

|---------|--------|

| 0       | 6      |

| 1       | 7      |

| 2       | 7      |

| 3       | 6      |

| 4       | 4      |

| 5       | 3      |

| 6       | 3      |

| 7       | 4      |

この場合のセレクタ12の出力およびリタイミング・フリップ・フロップ50の出力は⑦'および⑧'に示される通りである。リタイミング・フリップ・フロップ50の出力®'を縦軸に遅延をとって示すと⑨'に示される如くになる。このジッタの内容は、中心となる位相遅延はクロックAの7周期分、ジッタ振幅はピーク・ピーク値でクロックAの4周期分、そしてジッタ周期はクロックAの80周期分の近似正弦波ジッタである。